Implementation of Digital Clock using Spartan3an FPGA Evaluation Kit

Call for Price

Electronic clocks have predominately replaced the mechanical clocks. They are much reliable, accurate, maintenance free and portable. In general, there are two kinds of electronic clocks.

Description

Abstract

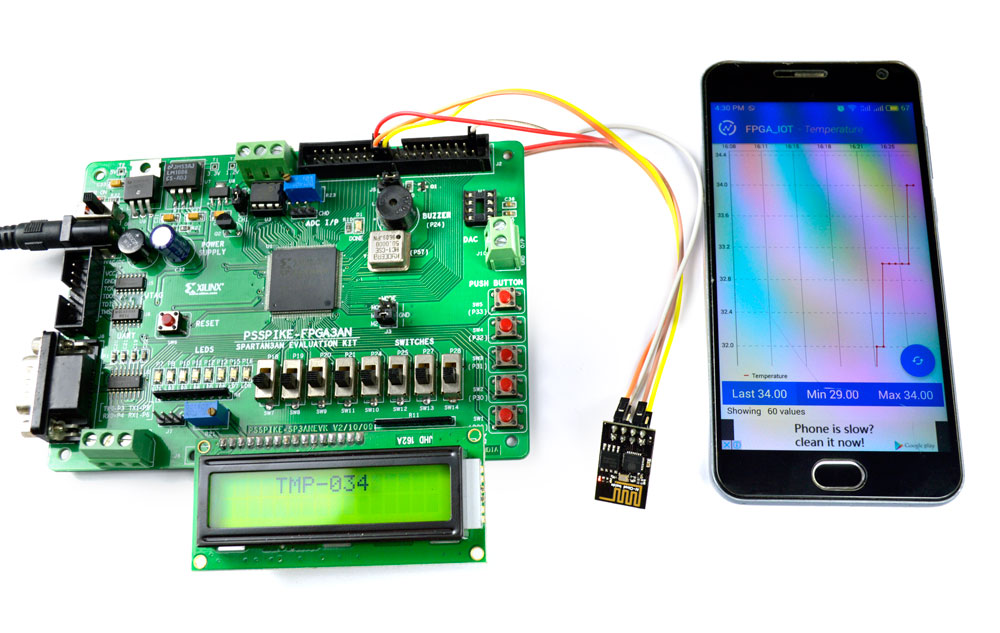

Electronic clocks have predominately replaced the mechanical clocks. They are much reliable, accurate, maintenance free and portable. In general, there are two kinds of electronic clocks. They are analog clock and digital clock. But digital clocks are more common and independent of external source. It would be needed the controlled devices and implementation of software for microcontroller control system because the hardware devices cannot do any desired task to execute. In this paper, the Spartan3an FPGA based digital clock is constructed with XC3S50an and its software program is written with VHDL language. Various types of digital clocks and modules are available in the market nowadays but this clock is different at least in the accurate time. To be controlling in FPGA is only the feature of the clock. The input frequency is taken from the 50 Hz clock frequency circuit. To show the time, 2×16 LCD is used.

Demonstration Video

Tool required

Software:

- Xilinx ISE 10.1i or above

Language:

- VHDL

Hardware:

- Spartan3an Project Kit.

- LCD Module

- JTAG Cable

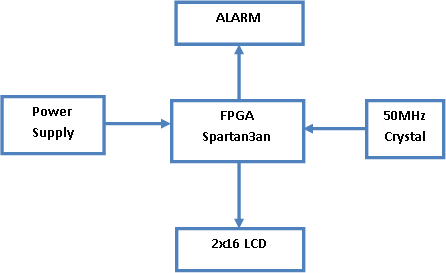

Block Diagram for Implementation of Digital Clock using Spartan3an FPGA Evaluation Kit

Pin Assignment with Spartan3an

LCD and Clock XC3S50-Pins

| RS | P105 |

| RW | P104 |

| E | P103 |

| D0 | P102 |

| D1 | P101 |

| D2 | P99 |

| D3 | P98 |

| D4 | P96 |

| D5 | P93 |

| D6 | P92 |

| D7 | P91 |

| CLK | P57 |

Introduction:

TIME is such a fundamental concept that it is very difficult to define. To measure time is needed something that will repeat itself at regular intervals. The number of intervals counted gives a quantitative measure of the duration. The earliest references for the measurement of the time are the moon and sun. When the sun and the moon were not visible, it was impossible to know the exact time. So, clocks were developed to measure out the hours between checks with the sun and the moon. The process of measuring time has progressively become more accurate, and the devices more localized ever since. In our modern time, the time is predominately measured by mechanical, and recently by electronic clocks. All clocks measure time, but different clocks can have status or importance. Many centuries have been spent devising method for the determination and measurement of time. Historically, clocks and watches of all sorts lie at an important crossroads of science, technology and society. Changes in timekeeping technology have influenced the character of scientific observation, aided the development of other machine technologies and brought significant revisions in the way people think about and behave in time. In this paper, the more accurate clock using FPGA is presented.

Design Consideration for Implementation

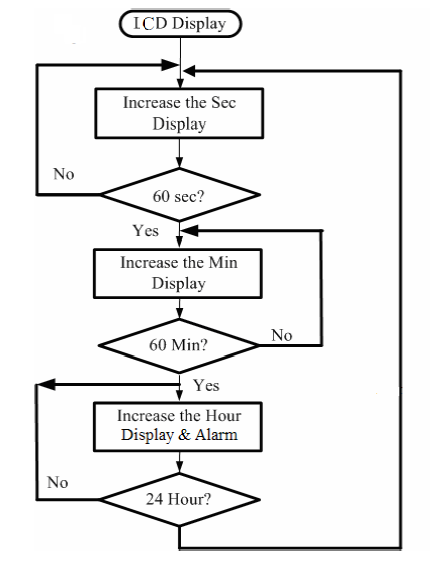

In the software implementation process, initialization processing, LCD display processing, time adjustment processing and time signal processing are considered.

In this paper, the FPGA-based digital clock is mainly controlled by the clock pulse frequency. The clock pulse frequency can be generated by using the 50 MHz Crystal. Every one hour is indicated by Buzzer indicator.

Flowchart for Digital Clock Display

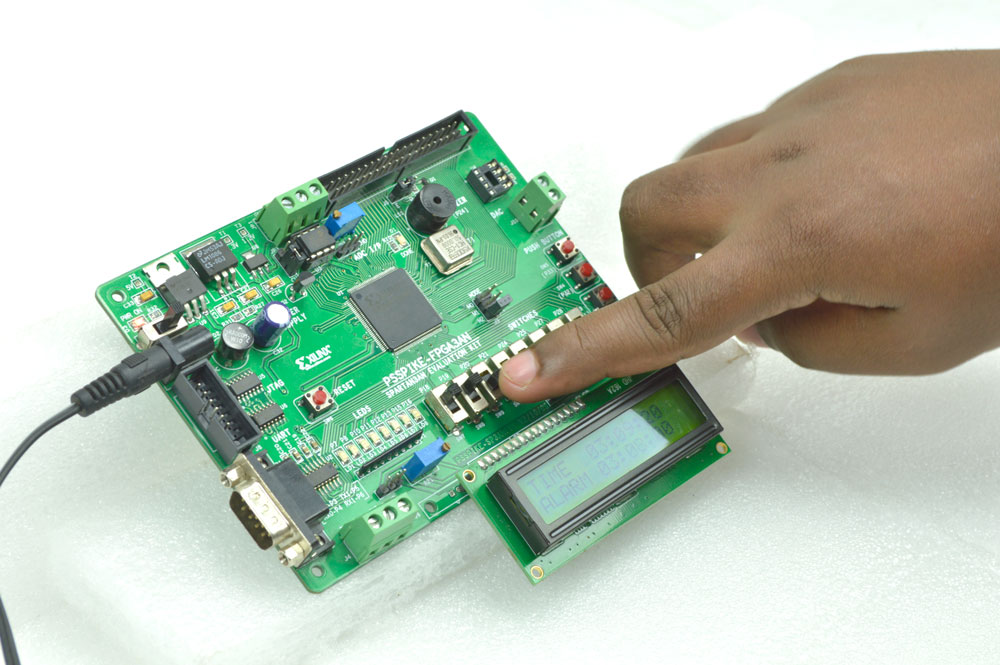

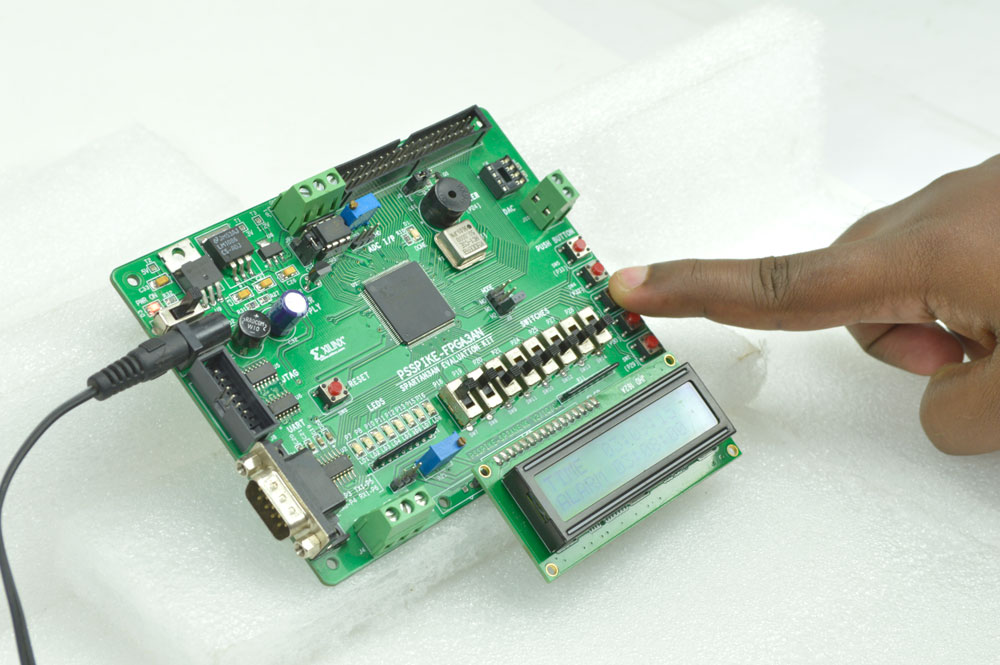

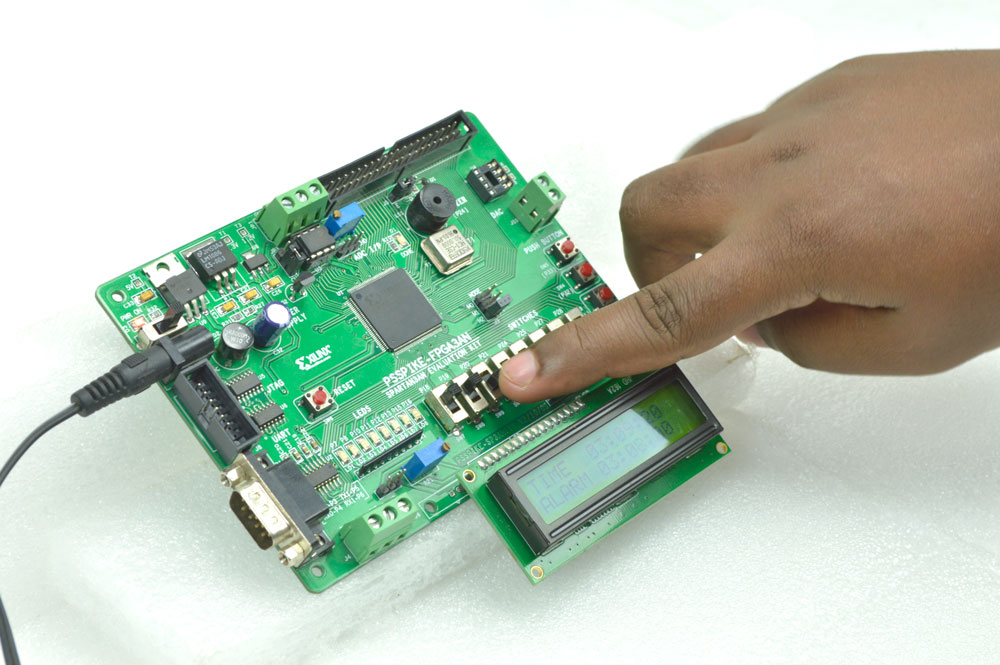

Spartan3an FPGA Evaluation Board LCD Placement

Source Code

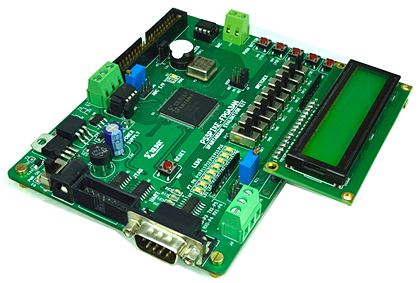

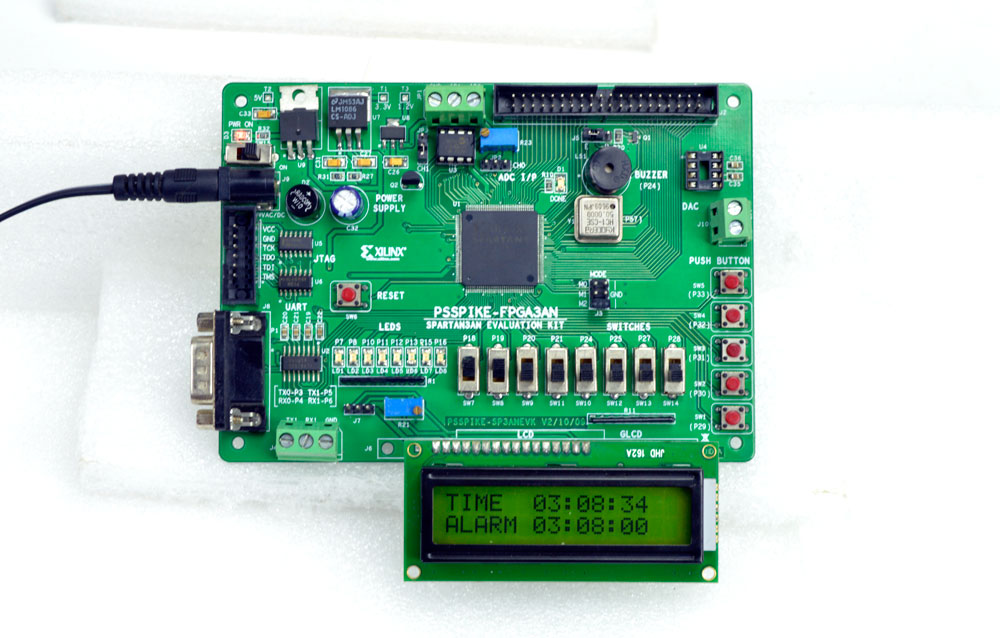

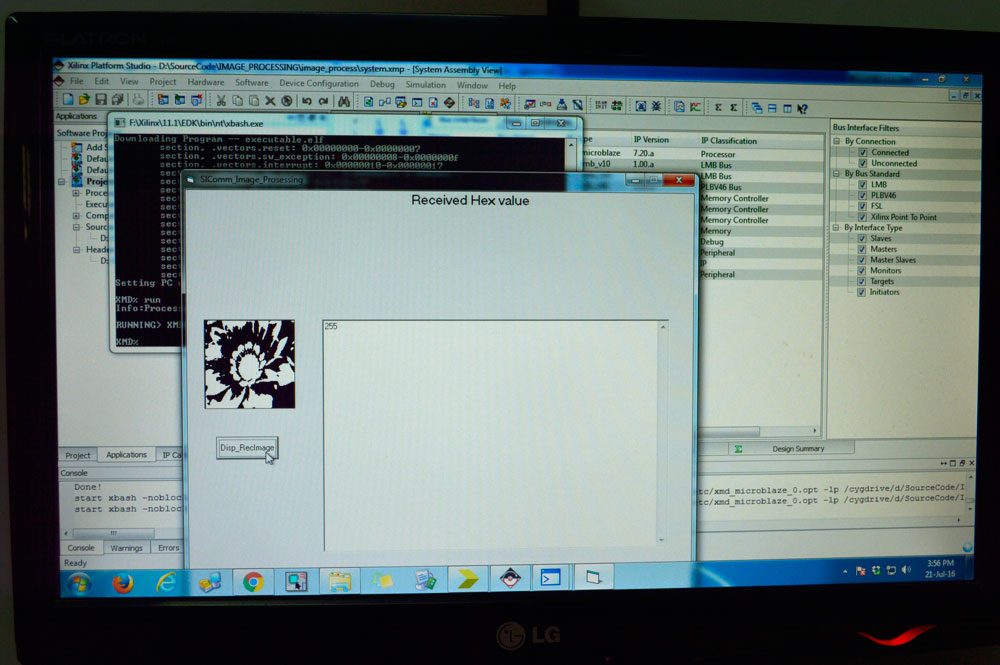

Digital Clock using Output Image

Conclusion

The Spartan3an FPGA Evaluation Kit based digital clock is mainly controlled by the clock pulse frequency. The clock pulse frequency can be generated by using the 50 MHz Crystal. Every one hour is indicated by Buzzer indicator.

Additional information

| Weight | 1.000000 kg |

|---|

Reviews

There are no reviews yet.