Slide switch and Push Button interfacing with Spartan3a FPGA Project Kit

slide switch and Push Button interfacing with Spartan3a FPGA Project Kit

Slide switch

Slide switches are most common used in electronic circuits for digital input of ON/OFF states. They allow control over current flow in a circuit. You’ll usually find slide switches in SPDT or DPDT configurations.

Push Buttons

Push-button switches are the classic momentary switch. Typically these switches have a really nice, tactile feedback when you press them.

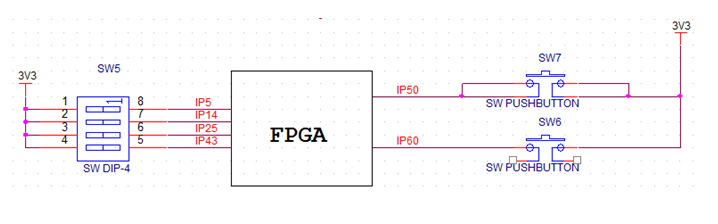

Schematic to interface Slide Switch and Push Button with Spartan3a FPGA Project Kit

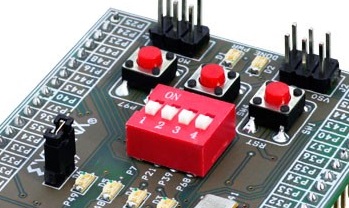

Slide Switch and Push Button Placement in Spartan3a FPGA Project Kit

Interfacing Slide Switch and Push Button with Spartan3a FPGA Project Kit

Push Button interface is straight forward. One end of Push Button connected to FPGA and another end connected to ground. Slide switch interface to FPGA is Pulled High by default at open end and another end is connected to ground which act as OFF State.

VHDL Code for Slide Switch Interfacing with spartan3a FPGA Project Kit

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity pb_led is

Port ( pb : in STD_LOGIC_VECTOR (1 downto 0);

led : out STD_LOGIC_VECTOR (3 downto 0));

end pb_led;

architecture Behavioral of pb_led is

begin

process(pb)

begin

if pb = "01" then

led <= "01010101";

elsif pb = "10" then

led <= "10101010";

elsif pb = "11" then

led <= "11111111";

else

led <= "00000000";

end if;

end process;

User Constraint File

NET "led[3]" LOC = P49; NET "led[2]" LOC = P48; NET "led[1]" LOC = P44; NET "led[0]" LOC = P43; NET "pb[1]" LOC = P43 | Pulldown; NET "pb[0]" LOC = P44 | Pulldown;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity pb_led is

Port ( pb : in STD_LOGIC_VECTOR (1 downto 0);

led : out STD_LOGIC_VECTOR (3 downto 0));

end pb_led;

architecture Behavioral of pb_led is

begin

process(pb)

begin

if pb = "01" then

led <= "01010101";

elsif pb = "10" then

led <= "10101010";

elsif pb = "11" then

led <= "11111111";

else

led <= "00000000";

end if;

end process;

end Behavioral;

User Constraint File

NET "led[3]" LOC = P49; NET "led[2]" LOC = P48; NET "led[1]" LOC = P44; NET "led[0]" LOC = P43; NET "pb[1]" LOC = P43 | Pulldown; NET "pb[0]" LOC = P44 | Pulldown;