FPGA Implementation of Tertix Game using Spartan3 FPGA Image Processing kit

Call for Price

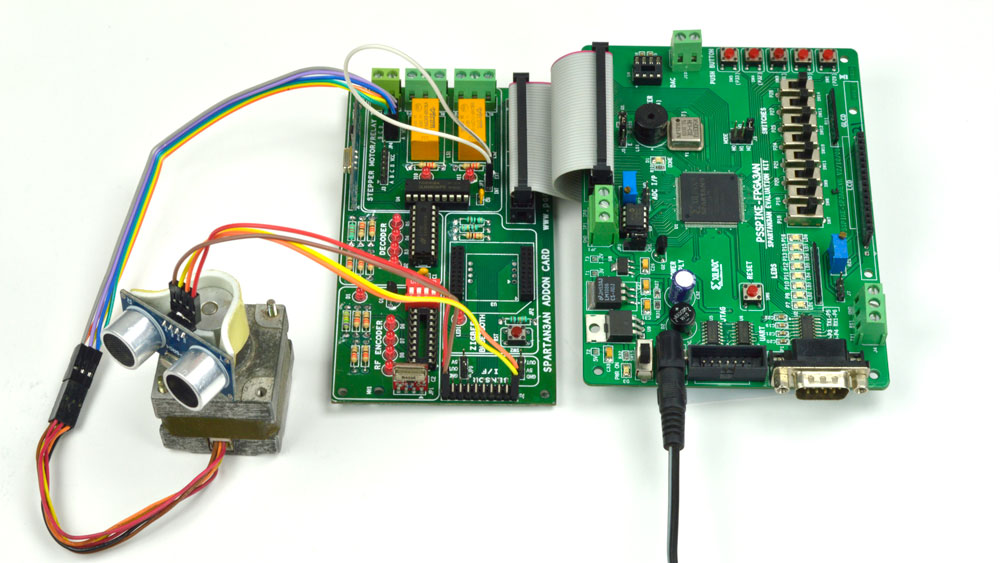

This Project presents the design of a circuit of a playable video game: tetrix. The project requires a Spartan3 FPGA Image Processing kit which is connected to a keyboard (PS2 port) and a monitor (VGA port).

Description

Abstract

This Project presents the design of a circuit of a playable video game: tetrix. The project requires a Spartan3 FPGA Image Processing kit which is connected to a keyboard (PS2 port) and a monitor (VGA port). The game is controlled from the keyboard and can be watched on the monitor, the screen is also showing a textbox in which is displayed the topscore, the player’s score and the keyboard keys which are used to play the game.

The project contains reusable components: 3 different type of keyboard scan code reader, vga signal generator and 2 different type of character generator.

The design is complete, meets all requirements, and it has been verified through component simulations and physical implementation. Here I must tell that the “gamecontrol” component is a little unstable, almost every changes in this component drives to bad compilation.

The circuit is defined in VHDL, and it targets a Xilinx Spartan-3E FPGA. Since all source files are VHDL, they can be used on other type of Xilinx FPGAs. The circuit was designed using the Xilinx 11.1i CAD tool.

Demonstartion Video

Tool required

Software: Xilinx ISE 11.1i

Language: VHDL

Hardware:

1. Spartan3 FPGA Image Processing kit

2.Monitor

3.Keyboard

Block Diagram

Introduction

The design uses the PS2 port, a two-wire serial bus (including clock and data) to communicate with the keyboard and the VGA port, the five standard VGA signals Red(red), Green(grn), Blue(blu), Horizontal Sync (hs) and Vertical Sync(vs).

Design

The Tetrix was designed for Xilinx XC3S200 FPGA with 200K gates, but it should work with other Xilinx FPGAs.The design’s operating frequency is 50MHz.

To play the game push the F2 button, when the game is running you can’t use the F2 button, to begin a new game you must end it first or push the stop button(F1). The game is very similar with the Tetrix found on the internet: it has 5 different objects which you can rotate and move to left or right.

|

Signal |

Mode |

Description |

|

mclk |

Input |

Main clock input |

|

kc |

Input |

Keyboard clock |

|

kd |

Input |

Keyboard data |

|

blu |

Output |

VGA Blue signal |

|

grn |

Output |

VGA Green signal |

|

hs |

Output |

VGA Horizontal Sync |

|

red |

Output |

VGA Red signal |

|

vs |

Output |

VGA Vertical Sync |

The game has 4 different speeds and the speed will be increased by the score:

Pushing the S button will increase the speed until the block reaches the bottom.

|

Speed |

Score |

|

1 |

<100 |

|

2 |

100<,<200 |

|

3 |

200<,<300 |

|

4 |

300< |

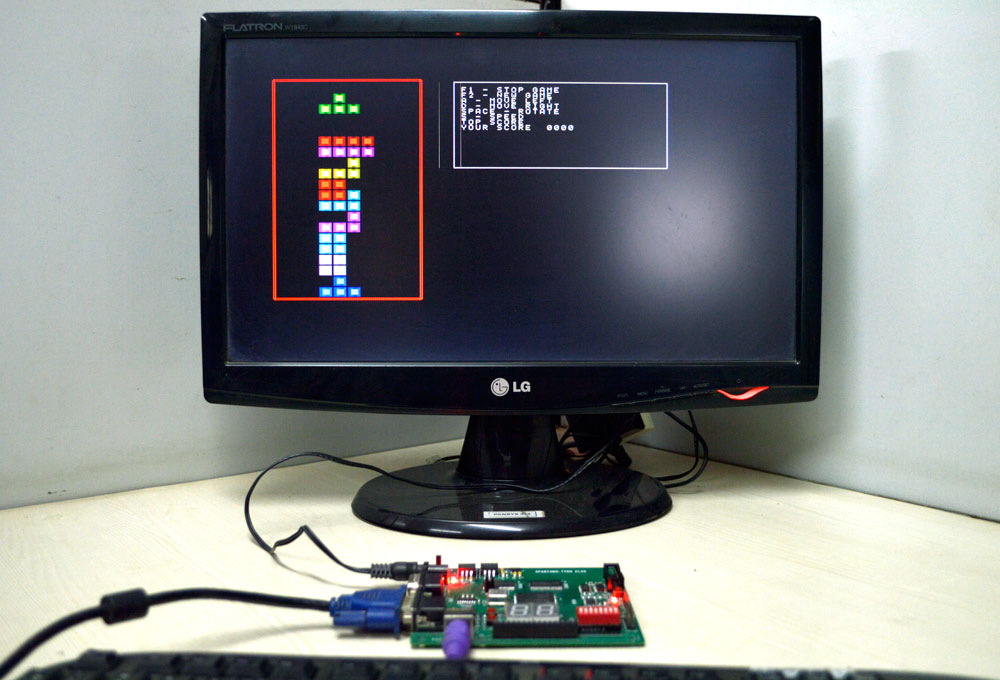

The image below shows the actual game running on the screen

As you can see the screen contains 2 different type of objects: a textbox at the right and the tetrix at the left. I am using 2 Block RAMs in which I keep the dates. The textbox contains 32×16=512 characters and each character is kept in a 8 bit code, so here was necessary to use a BlockRAM.I used another BlockRam at the tetrix part, this wasn’t necessary and the making of the “gamecontrol” become very complicated(you could access only 1 block once in a clock). The “tetrix“ is made by 10×20 blocks and each is memorized in 4 bits(first bit is telling if there is something or not and the other 3 is keeping the block’s color).This means that we can draw only 8 different kind of colors(red, green, blue, yellow, black, white, aqua, fuchsia), but this is not true. If you look more carefully at the image you will see that I have more than 8 colors. To generate more colors you take the 50MHz and divide it to 25MHz,12.5MHz, 6.25MHz and make different kind of PWMs using this clocks. With this PWMs you can draw 4913 different colors or more.

On the next page you can see the RTL Schematic of the design. I am using dual-port BlockRAMs, the components from the left side of the rams are using the A ports to read and write, the components from the right side of the rams are using the B ports and they only read, they don’t write in it. The two sides are working independently from each other, the left side is the game control part and the right side is the vga control part.

The schematic can be divided horizontally too, the upper half is accessing the tetrix’s ram and they are controlling the game, while the lower half is controlling the textbox and the score of the game.

State diagram for Tetrix Game Implementation

Conclusion

FPGA based Tetrix Game controller designed and implemented in Spartan3 FPGA Image Processing kit and game played with keyboard and monitor interfacing.

Additional information

| Weight | 1.000000 kg |

|---|

Reviews

There are no reviews yet.